## CONCURRENT TECHNOLOGIES

The dark powers on Intel<sup>®</sup> processor boards

#### **Processing Resources (3U VPX)**

#### **Boards with Multicore CPUs:**

> Up to 16 cores using Intel<sup>®</sup> Xeon<sup>®</sup> D-1577 on TR C4x/msd

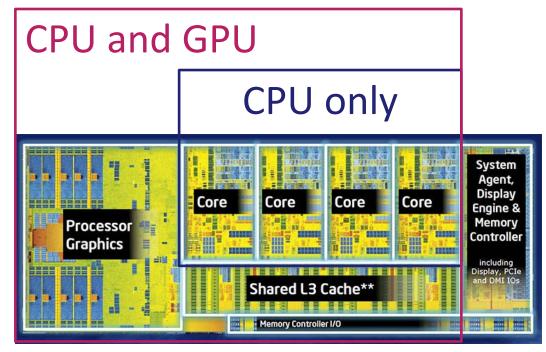

Boards with 4-Core CPUs and Multiple Graphical Execution Units:

> Up to 72 cores using Intel® Xeon® E3-1515M v5 on TR E5x/msd

#### Board types need radically different solutions:

> There isn't just an Intel SBC anymore

#### Intel marketing is very inventive

#### There is a bewildering range of Technologies and kits

- Intel Turbo Boost Technology

- Intel Hyper Threading Technology

- Intel Virtualization Technology (VT-x)

- Intel Virtualization Technology for Directed I/O (VT-d)

- > Intel VT-x with Extended Page Tables (EPT)

- > Intel TSX-NI

- Enhanced Intel SpeedStep® Technology

- > Trusted Execution Technologies

- Intel vPro Technology

- Intel Data Plane Development Kit (DPDK)

- Intel Media Server Studio SDK.....etc

#### What does this mean for our typical users?

#### 譅 TSX-NI

- **Resource and Cache Allocation**

- Intel Media Server Studio 2016

#### **TSX-NI**

- Transactional Synchronization Extensions New Instruction

- Designed to improve high-performance computing (HPC) workloads

- Enables optimistic execution of transactional code regions with hardware 'roll-back' when multiple threads access a conflicting memory section

- Easy to implement

- **Can provide significant performance benefits:**

- > Up to 40% on real world HPC workloads

#### TSX-NI now available on mobile chipsets

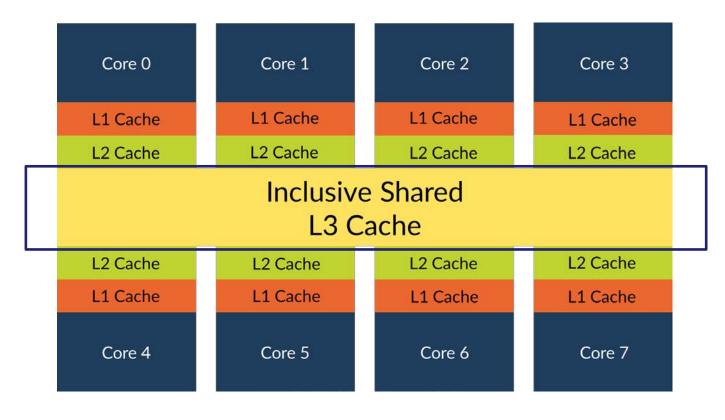

#### **Resource Allocation Strategies**

#### **Original Single Board Computer:**

> OS and application ran on a single core

#### Modern Control Applications:

- Single OS per board

- > OS typically schedules an application to use all available CPU cores

#### Modern Server Applications:

- > Multiple OS per board using bare metal or hosted virtualization

- > Virtual Machines are allocated a fixed number of CPU cores and memory

#### **Resource Allocation**

#### **Some observations on Virtualization:**

- Stable technology, data centre market mature

- > Not as low cost as you might want (Physicalization!)

- > Very attractive for embedded server applications with SWaP restrictions

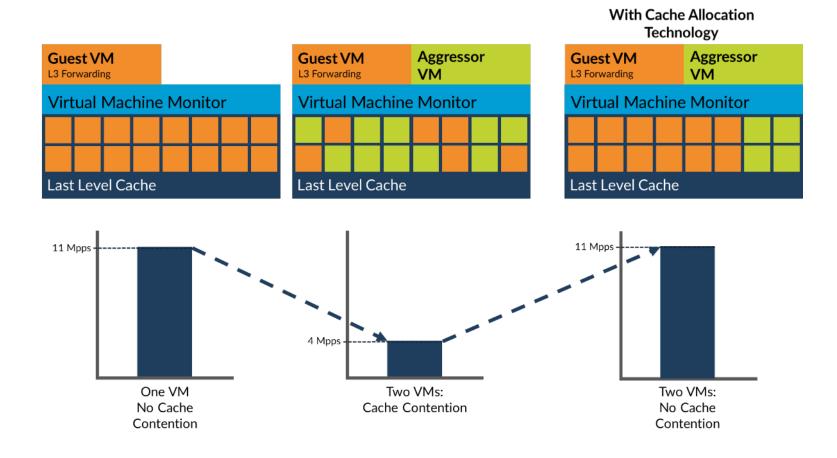

- > Can affect performance when Virtual Machines contend for L3 cache space

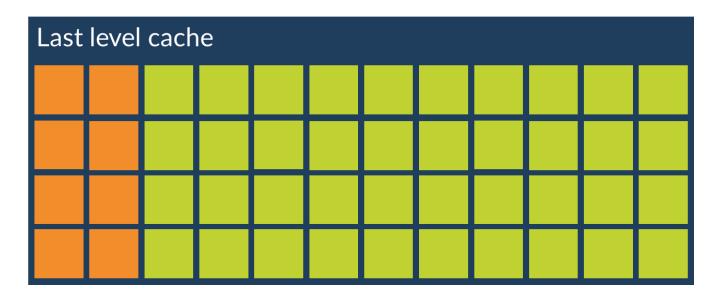

#### **Cache Monitoring Technology (CMT)**

- **Shows L3 cache allocation by Virtual Machine**

- **Identifies low priority tasks are consuming too much L3 Cache**

- **Known as 'Noisy Neighbor' syndrome**

| Last level cache |  |  |  |  |  |  |  |  |  |  |  |

|------------------|--|--|--|--|--|--|--|--|--|--|--|

|                  |  |  |  |  |  |  |  |  |  |  |  |

|                  |  |  |  |  |  |  |  |  |  |  |  |

|                  |  |  |  |  |  |  |  |  |  |  |  |

|                  |  |  |  |  |  |  |  |  |  |  |  |

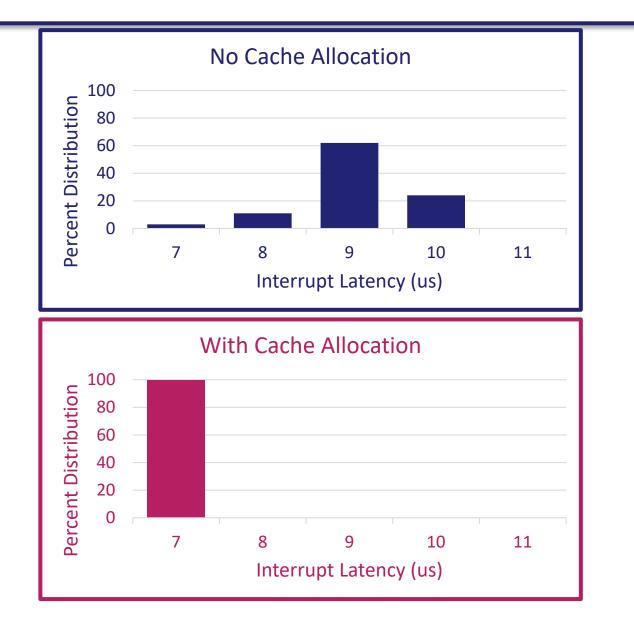

#### **Cache Allocation Technology (CAT)**

- **CAT allows intelligent L3 cache partitioning**

- High priority tasks can be allocated more L3 cache

- **Improves determinism**

#### **Improves Consistency**

Without cache allocation the noisy neighbor causes the latency to vary

With cache allocation the solution becomes more deterministic

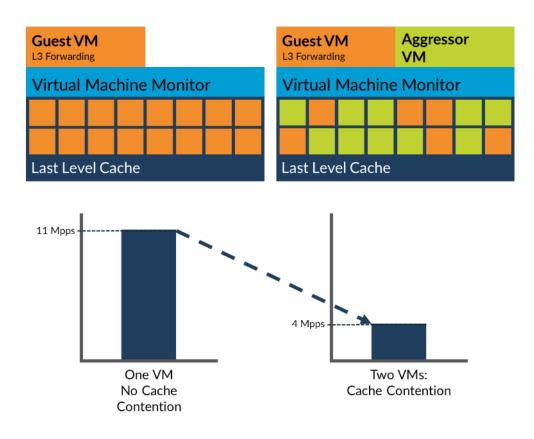

#### Throughput

- A single Virtual Machine runs a packet processing application consisting of a classification and scheduling stage

- This delivers 11 million packets per second (Mpps) of 64-byte packet throughput

#### Throughput

When a noisy neighbor Virtual Machine is introduced which takes a substantial portion of L3 cache, packet-processing application performance drops to 4 Mpps

#### Throughput

Limiting the aggressor VM's access to L3 cache, allows the packetprocessing application performance to revert to the original 11 Mpps

#### **Using Intel Media Server Studio 2016 SDK**

CONCURRENT Soft TECHNOLOGIES

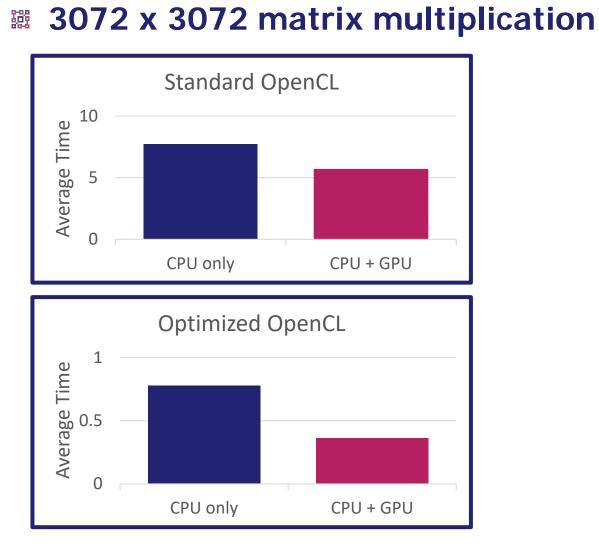

Intel: Haswell Processor

Board used AM C1x/msd, 4-core i7-4700EQ, 2.4GHz Comparing standard C code, standard OpenCL code, Intel optimized OpenCL code and OpenBLAS scientific library Full details available from Concurrent Technologies

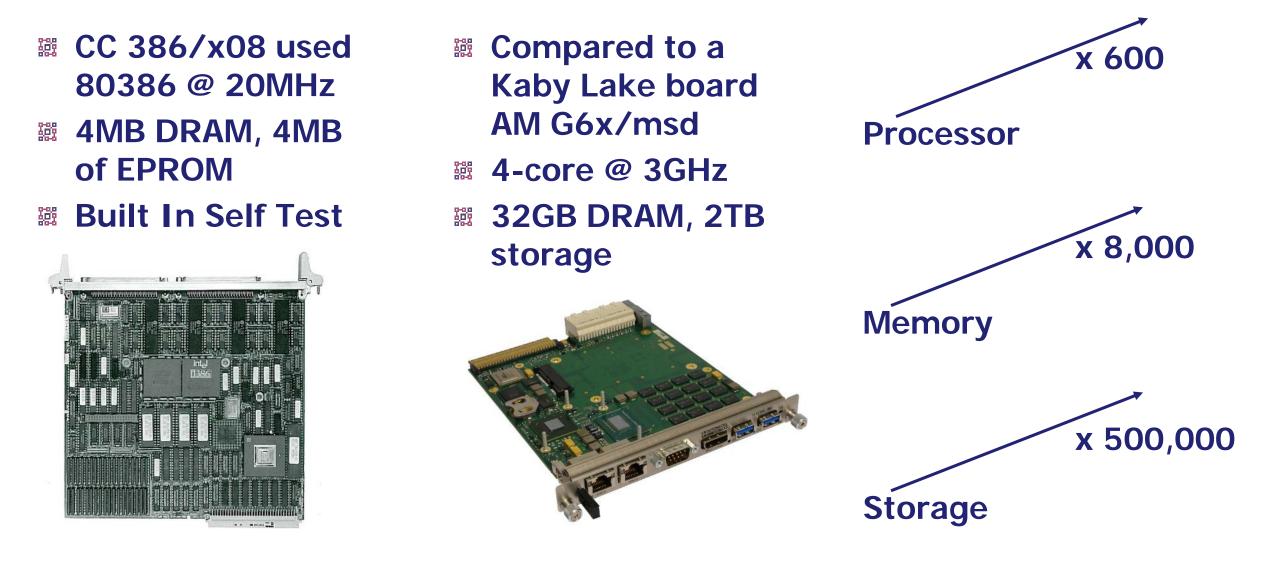

#### How far have we come since 1990?

CONCURRENT Soft TECHNOLOGIES

# **CONCURRENT TECHNOLOGIES**

### **Thanks for listening**